- 您现在的位置:买卖IC网 > Sheet目录1994 > DS1746-70IND (Maxim Integrated Products)IC RTC RAM Y2K 5V 70NS 32-EDIP

DS1746/DS1746P Y2K-Compliant, Nonvolatile Timekeeping RAMs

12 of 16

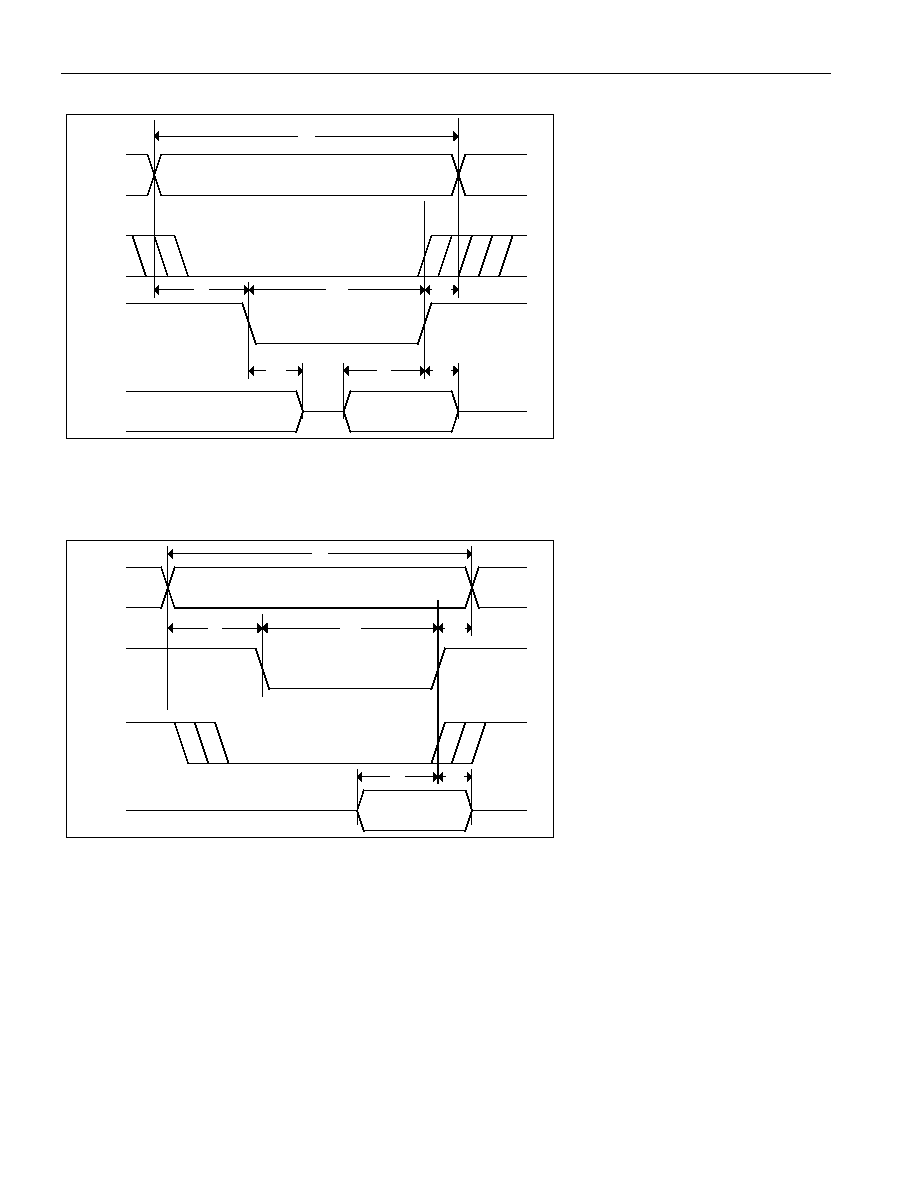

WRITE CYCLE TIMING DIAGRAM, WRITE-ENABLE CONTROLLED

tWC

t

WR1

t

DS

t

AS

t

WEZ

t

DH1

DATA INPUT

DQ0-DQ7

WE

CE

A0-A16

DATA OUTPUT

t

WEW

VALID

WRITE CYCLE TIMING DIAGRAM, CHIP-ENABLE CONTROLLED

t

WC

t

WR2

tDS

tDH2

t

AS

DATA INPUT

WE

CE

A0-A16

t

CEW

VALID

DQ0-DQ7

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DS1747W-120IND

IC RTC RAM Y2K 3.3V 120NS 32EDIP

DS17887-3-IND

IC RTC 3V 8K NV RAM 24-EDIP

DS1851E-010+

IC DAC DUAL NV TEMP CNTRL 8TSSOP

DS2187S+

IC RECEIVE LINE INTERFACE 20SOIC

DS21Q58L

IC TXRX E1 QUAD 3.3V 100-LQFP

DS2404B

IC ECONORAM TIMECHIP 5.5V 16SSOP

DS2415P+T&R

IC TIME CHIP 1-WIRE 6-TSOC

DS2417X/T&R

IC TIMECHIP W/INTRPT 1WIRE CSP

相关代理商/技术参数

DS1746-70IND+

功能描述:实时时钟 Timekeeping NV RAM RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1746P

制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:Y2K-Compliant, Nonvolatile Timekeeping RAMs

DS1746P/YP/WP

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:PowerCap with Crystal

DS1746P-70

功能描述:实时时钟 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1746P-70+

功能描述:实时时钟 Timekeeping NV RAM RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1746P-70IND

功能描述:实时时钟 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1746P-70IND+

功能描述:实时时钟 Timekeeping NV RAM RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1746W

制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:Y2KC Nonvolatile Timekeeping RAM